- How to Adjust X and Y Axis Scale in Arduino Serial Plotter (No Extra Software Needed)Posted 7 months ago

- Elettronici Entusiasti: Inspiring Makers at Maker Faire Rome 2024Posted 7 months ago

- makeITcircular 2024 content launched – Part of Maker Faire Rome 2024Posted 9 months ago

- Application For Maker Faire Rome 2024: Deadline June 20thPosted 10 months ago

- Building a 3D Digital Clock with ArduinoPosted 1 year ago

- Creating a controller for Minecraft with realistic body movements using ArduinoPosted 1 year ago

- Snowflake with ArduinoPosted 1 year ago

- Holographic Christmas TreePosted 1 year ago

- Segstick: Build Your Own Self-Balancing Vehicle in Just 2 Days with ArduinoPosted 1 year ago

- ZSWatch: An Open-Source Smartwatch Project Based on the Zephyr Operating SystemPosted 1 year ago

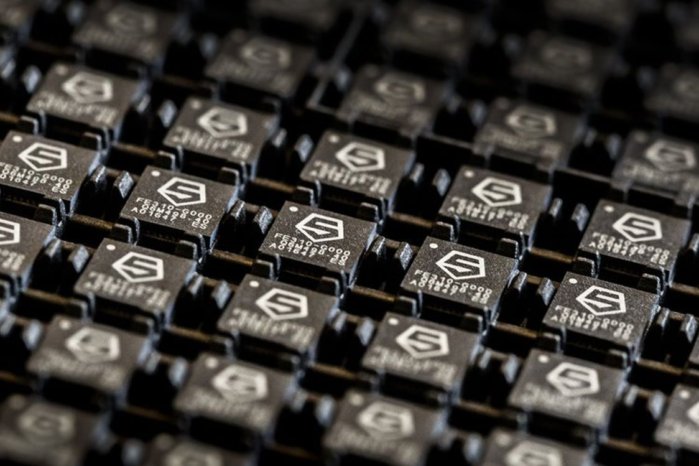

SiFive Coreplex IP designs have become the leader for RISC-V cores

The RISC-V open-source architecture, created by researchers at the University of California, Berkeley, in 2010, is open to all who want to use it. The RISC-V design can be modified for PCs, servers, smartphones, wearables, and other devices.

RISC-V shares the ethos of open-source software, with the community working together to share, advance, and modify the architecture.

Since the project’s inception, the interest in RISC-V has ballooned, with some of the big IT companies (like Google, Nvidia, AMD, Microsoft…) showing interest in the architecture.

A startup called SiFive is the first to make a business out of the RISC-V architecture. The company is also the first to convert the RISC-V instruction set architecture into actual silicon. SiFive’s Coreplex IP has demonstrated significantly better power efficiency compared to other, competing ISAs (open RISC-V instruction set architecture).

SiFive few days ago revealed two initial Coreplex design configurations:

- E31 Coreplex – The most deployed RISC-V core in the world, the E31 Coreplex is designed for low power, high performance, 32-bit embedded applications such as Edge Computing, Smart IoT or Wearables.

- E51 Coreplex: A 64-bit embedded core, the E51 Coreplex is the ideal solution to act as a system or host control core inside larger 64-bit SoCs, as its small size and performance efficiency set it apart from the typical, bloated and large 64-bit processors while still maintaining full software compatibility with mainstream toolchains.

The RISC-V Foundation has aggressively promoted the architecture, because it has a different design than the highly integrated x86, Power, and to an extent, the ARM designs. It’s modular, meaning that independent co-processing circuits can be attached to the central RISC-V design. For example, a security or networking coprocessor can be tacked onto the core design. That makes the RISC-V highly flexible.